Learn extra at:

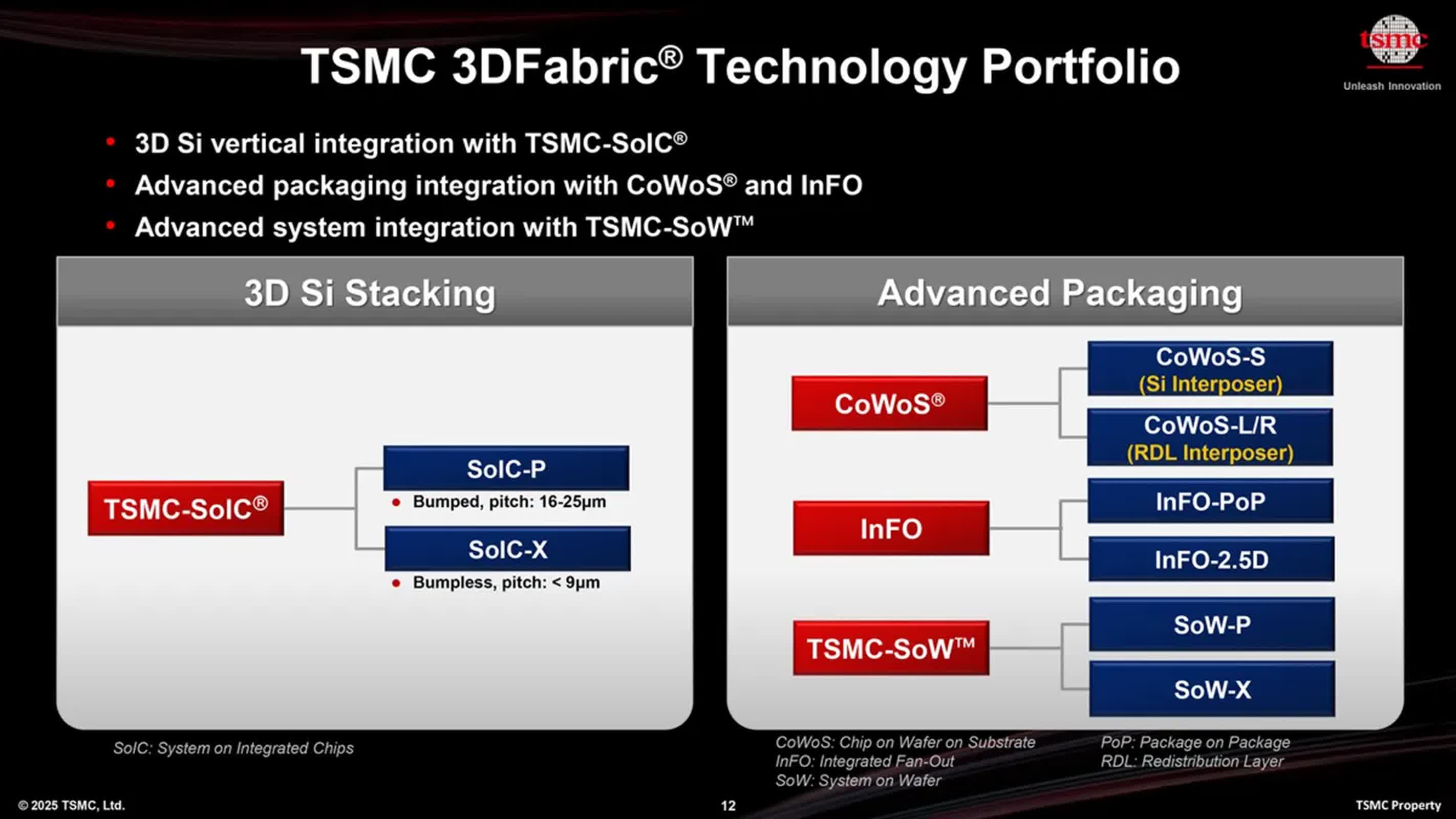

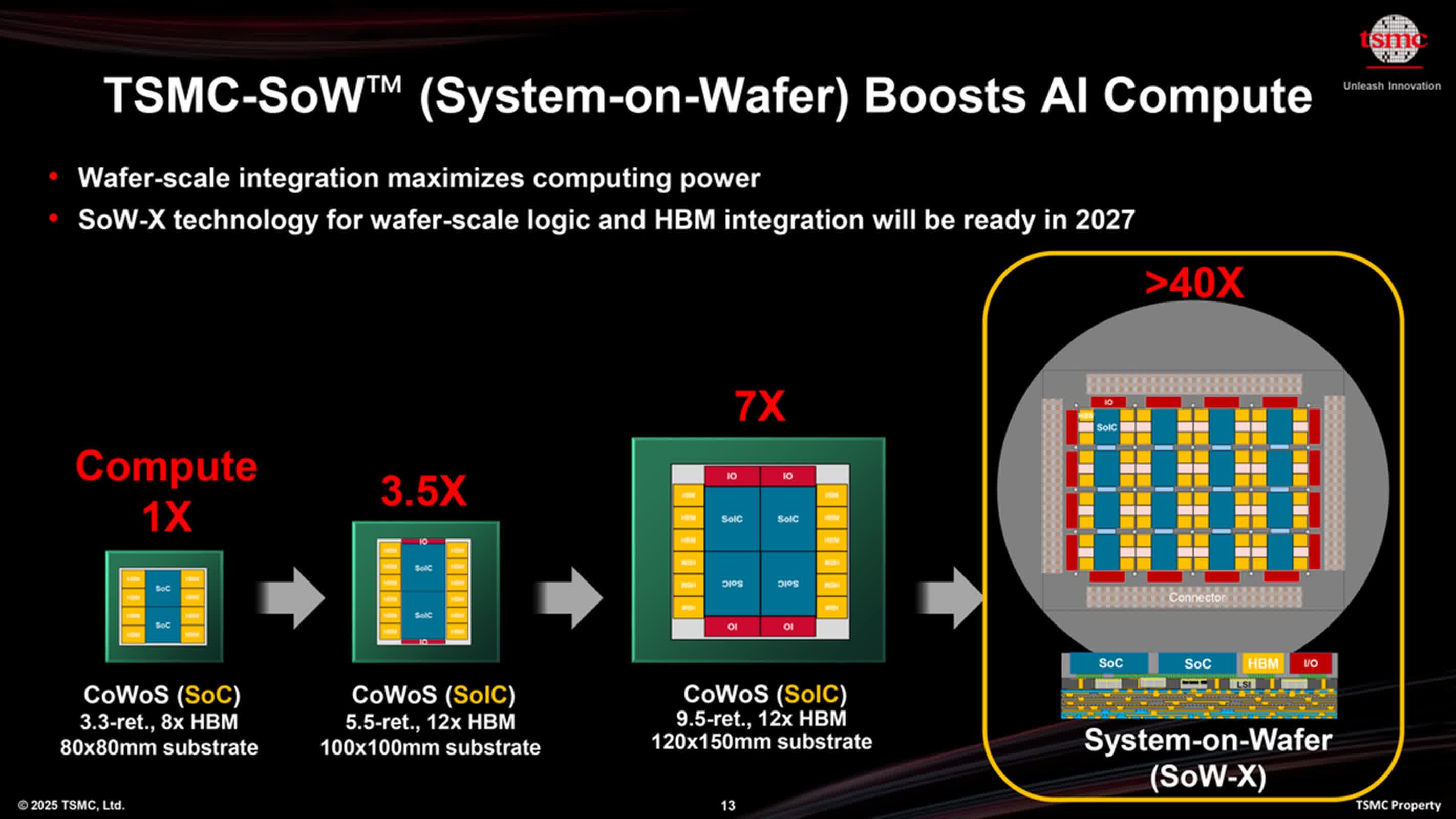

The large image: The semiconductor trade is approaching a big milestone as TSMC prepares to broaden the bodily scale of its chip packaging know-how. At its current North American Know-how Symposium, the corporate detailed plans for a brand new era of CoWoS (Chip-on-Wafer-on-Substrate) know-how, enabling the meeting of multi-chiplet processors a lot bigger than these at the moment in manufacturing.

At this time’s high-end processors, particularly these powering knowledge facilities and AI workloads, already depend on multi-chiplet designs to fulfill hovering calls for for efficiency and reminiscence bandwidth. TSMC’s present CoWoS options can accommodate interposers as much as 2,831 mm², greater than thrice the dimensions of a typical photomask reticle, which is proscribed to 830 – 858 mm² by EUV lithography constraints.

This know-how is already being utilized in merchandise like AMD’s Intuition MI300X and Nvidia’s B200 GPUs, which mix giant compute chipsets with stacks of high-bandwidth reminiscence.

Nonetheless, as AI and high-performance computing purposes proceed to develop in complexity, the urge for food for much more silicon is barely rising. To handle this, TSMC is developing a brand new CoWoS-L packaging know-how, set to launch as early as subsequent yr, supporting interposers as giant as 4,719 mm² – about 5.5 instances the reticle restrict – and require substrates measuring 100×100 mm. This can permit as much as 12 stacks of high-bandwidth reminiscence, a big step up from present capabilities.

TSMC initiatives that chips constructed with this know-how will ship greater than three and a half instances the compute efficiency of immediately’s main designs, probably assembly the wants of upcoming processors like Nvidia’s Rubin GPUs.

Trying additional, TSMC plans to push the envelope with an excellent bigger package deal: a 7,885 mm² interposer mounted on a 120×150 mm substrate, a footprint barely greater than a typical CD case. This represents a 9.5-fold improve over the reticle restrict and almost doubles the realm of the corporate’s earlier 8x-reticle package deal.

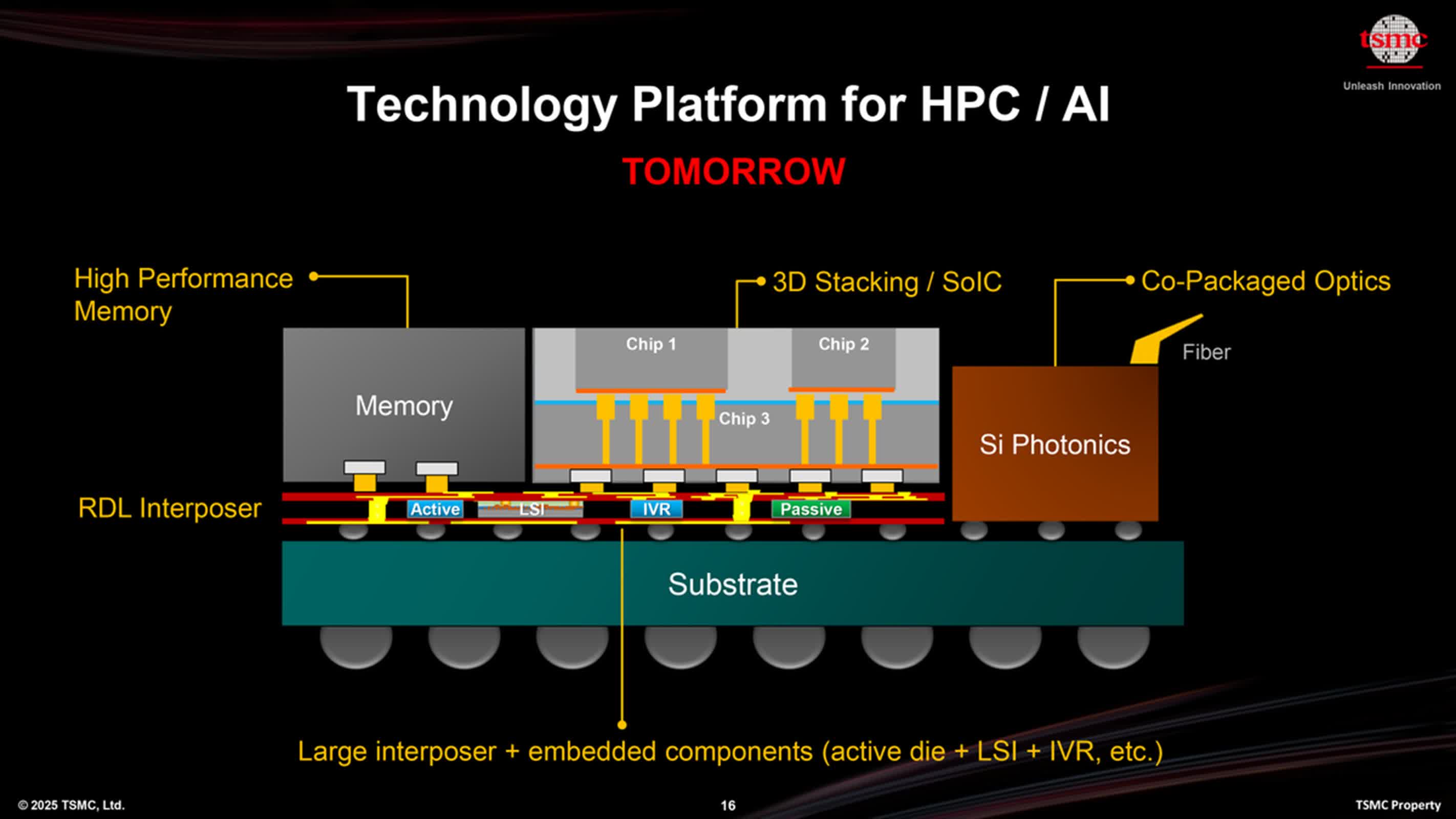

Such a large meeting may host 4 3D-stacked systems-on-integrated chips, twelve HBM4 reminiscence stacks, and a number of enter/output dies, setting a brand new benchmark for efficiency and integration.

For purchasers with essentially the most excessive efficiency necessities, TSMC can also be providing its System-on-Wafer (SoW-X) know-how, which allows the mixing of total wafers right into a single chip. Whereas just a few corporations, equivalent to Cerebras and Tesla, at the moment use wafer-level integration for specialised AI processors, TSMC anticipates broader adoption because the demand for super-sized chips grows.

The engineering challenges related to these behemoth processors are appreciable. Delivering energy to giant, multi-chiplet assemblies requires progressive options, as they will draw kilowatts of energy, far past what conventional server designs can deal with.

To deal with this, TSMC is integrating superior energy administration circuits instantly into the chip package deal. Utilizing its N16 FinFET know-how, the corporate embeds monolithic energy administration ICs and on-wafer inductors into the CoWoS-L substrate, permitting energy to be routed effectively by means of the package deal.

This strategy reduces electrical resistance and improves energy integrity, enabling dynamic voltage scaling and speedy response to altering workloads. Embedded deep trench capacitors additional stabilize electrical efficiency, filtering out voltage fluctuations and guaranteeing dependable operation underneath heavy computational masses.

These advances replicate a broader shift towards system-level co-optimization, the place energy supply, packaging, and silicon design are handled as interconnected parts reasonably than separate considerations.

Nonetheless, the transfer to ever-larger chip packages just isn’t with out its problems. The bodily dimension of the brand new substrates, significantly the 100×100 mm and 120×150 mm codecs, is pushing the bounds of present module requirements equivalent to OAM 2.0, and should require new system and board design approaches.

Thermal administration is one other important problem. As processors develop in dimension and energy consumption, they generate monumental quantities of warmth. {Hardware} producers are exploring superior cooling methods, together with direct liquid cooling and immersion, to maintain these chips working effectively.

TSMC has already labored with companions to develop immersion cooling options for knowledge facilities. These options can considerably cut back vitality consumption and stabilize chip temperatures, even underneath intense workloads. Nonetheless, integrating these cooling applied sciences instantly into chip packages stays a problem for the longer term.